## **GEN-2122-5**

# Quadrature Decoder/Counter/Shift Register Interface IC V2.0-071204

### **Features**

- Digital Input Filter

- · Quadrature Decoder

- 22 bit Up/Down counter

- 22 bit PISO Shift Register

- · Zero Reference mark support

- Counter Inhibit

- · Tristate bus output

- High Performance Maximum input speed of 10MHz

- 5V or 3.3V I/O Capability

- Samples are available

Package: 44 Pin PLCC

Operating Temperature Range: -20°C to 85°C

## **Description**

The GEN-2122-5 is a high-performance multi-purpose Interface IC. It contains a digital input filter and quadrature decoder with exposed outputs. This is also connected to a resettable 22-bit up/down counter and PISO shift register, allowing consistent extraction of the counter value with low interface pin counts.

#### Parameters:

| Parameter                                            | Min  | Max                     | Units |

|------------------------------------------------------|------|-------------------------|-------|

| V <sub>CCINT</sub> Supply voltage for internal logic | 4.75 | 5.25                    | V     |

| V <sub>CCIO</sub> Supply voltage for output drivers  | 4.75 | 5.25                    | V     |

|                                                      | 3.0  | 3.6                     |       |

| Low level input voltage                              | 0    | 0.8                     | V     |

| High level input voltage                             | 2.0  | V <sub>CCINT</sub> +0.5 | V     |

| Output Voltage                                       | 0    | V <sub>CCIO</sub>       | V     |

| Parameter                    | Test Conditions                 | Min | Max | Units |

|------------------------------|---------------------------------|-----|-----|-------|

| Output high voltage for 5V   | I= -4.0mA V <sub>CC</sub> = Min | 2.4 |     | V     |

| outputs                      |                                 |     |     |       |

| Output high voltage for 3.3V | $I=-3.2$ mA $V_{CC}=$ Min       | 2.4 |     | V     |

| outputs                      |                                 |     |     |       |

| Output low voltage for 5V    | I= 24mA V <sub>CC</sub> = Min   |     | 0.5 | V     |

| outputs                      |                                 |     |     |       |

| Output low voltage for 3.3V  | I= 10mA V <sub>CC</sub> = Min   |     | 0.4 | V     |

| outputs                      |                                 |     |     |       |

| Input leakage current        | V <sub>CC</sub> = Max           |     | ±10 | μA    |

|                              | $V_{IN}$ = GND or $V_{CC}$      |     |     |       |

| I/O high-Z leakage current   | V <sub>CC</sub> = Max           |     | ±10 | μA    |

|                              | $V_{IN}$ = GND or $V_{CC}$      |     |     | •     |

| I/O capacitance              | V <sub>IN</sub> = GND f= 1.0MHz |     | 10  | рF    |

## **Important Notice**

genapta decoders are not recommended for use in safety critical applications. eg: Life support systems, critical care medical equipment, ABS braking systems and power steering. Please contact us for clarification if required.

# Pin Assignments\*

| Pin | I/O | Name                  | Description                                                                                       |

|-----|-----|-----------------------|---------------------------------------------------------------------------------------------------|

| 2   |     | PL <sub>SR</sub>      | Shift Register Parallel Load                                                                      |

| 5   | I   | CLK <sub>QD</sub>     | Input from external clock source (max 32MHz).                                                     |

|     |     |                       | Determines maximum input speed for Quadrature                                                     |

|     |     |                       | Decoder and Input Filter.                                                                         |

| 6   |     | CLK <sub>SR</sub>     | Shift Register Clock                                                                              |

| 7   | l   | Z <sub>RST</sub>      | Zero reset. Rising edge turns Z <sub>DATA</sub> low. Z <sub>RST</sub> is                          |

|     |     |                       | asynchronous with respect to any other input                                                      |

|     |     | _                     | signal.                                                                                           |

| 9   | 0   | $Z_{DATA}$            | Zero data. Initially low, will go high on rising edge                                             |

|     |     | _                     | of Z <sub>IN</sub> , and remain high until a rising edge on Z <sub>RST.</sub>                     |

| 10  | -   | GND                   | GND                                                                                               |

| 11  | 0   | CNT <sub>DATA</sub>   | Count Data. Output from Shift Register                                                            |

| 21  | -   | V <sub>CCINT</sub>    | +5V                                                                                               |

| 23  | -   | GND                   | GND                                                                                               |

| 31  | -   | GND                   | GND                                                                                               |

| 32  | -   | V <sub>CCIO</sub>     | +5V/+3.3V - I/O Voltage                                                                           |

|     |     |                       | Quadrature input A                                                                                |

| 35  | I   | Α                     | A and B (pin 37) accept outputs from a quadrature encoded source, eg optical encoder. A and B are |

|     |     |                       | nominally +/- 90 degrees out of phase.                                                            |

|     |     |                       | Count up. Will pulse high for one clock cycle                                                     |

| 36  | 0   | CNT <sub>UP</sub>     | whenever the quadrature decoder detects a                                                         |

|     |     | OI TI OP              | upwards movement.                                                                                 |

| 37  | ı   | В                     | Quadrature input B (see pin 35)                                                                   |

|     | _   |                       | Inhibit any counter value change when high.                                                       |

| 38  | ı   | FREEZE                | Normal operation when low.                                                                        |

|     |     |                       | Zero/Reference mark input. Reset internal position                                                |

| 39  | I   | Z <sub>IN</sub> (RST) | counter to 0. Sets Z <sub>DATA</sub> . Z <sub>IN</sub> is asynchronous with                       |

|     |     |                       | respect to any other input signal.                                                                |

|     |     |                       | Chip Select, when high, CNT <sub>DATA</sub> , CNT <sub>UP</sub> ,                                 |

| 40  | I   | CS                    | CNT <sub>DOWN</sub> and Z <sub>DATA</sub> are undriven (tristate), when                           |

|     |     |                       | low, the pins drive their respective values.                                                      |

| 41  | -   | V <sub>CCINT</sub>    | +5V                                                                                               |

|     |     |                       | Count down. Will pulse high for one clock cycle                                                   |

| 43  | 0   | CNT <sub>DOWN</sub>   | whenever the quadrature decoder detects a                                                         |

|     |     |                       | downwards movement.                                                                               |

<sup>\*</sup>All other package pins should be tied to GND to ensure correct operation.

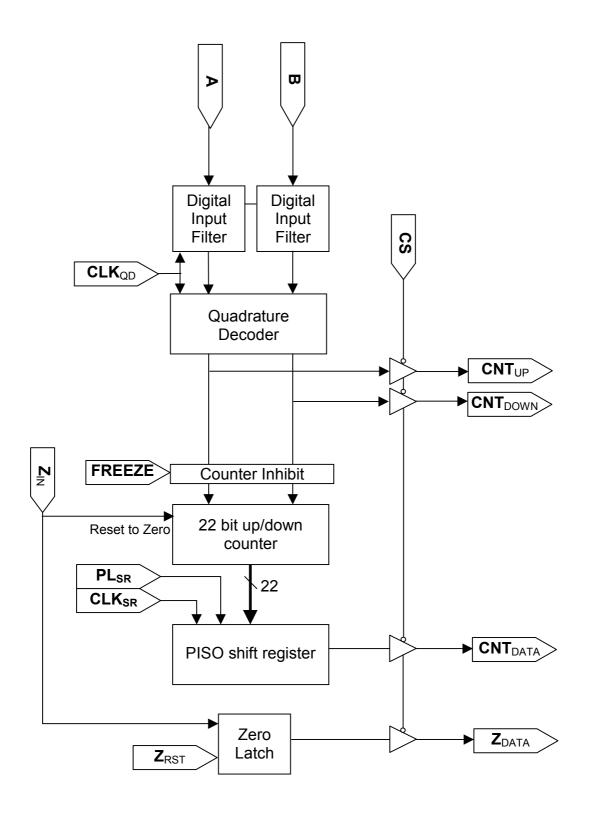

# **Functional Block Diagram:**

## **Component Description**

## **Digital Input Filter**

The digital input filter is responsible for removing noise from the incoming quadrature signals. A delay filter of 3 clock cycles rejects spikes of short duration. The input data is tested for a stable level being present for 3, and the filtered output will only change after the input signal has remained consistent for this time. Short noise spikes and pulses shorter than 2 clock periods are ignored.

The operation of the digital input filter places constraints on the maximum speed of input signals A and B. Because the signals must remain constant for 3 clock cycles, they can have an absolute maximum frequency of (CLK $_{\rm QD}$  / 3), and should be slower than this where noise is present. It is recommended that the input frequency is less than CLK $_{\rm QD}$  / 6.

#### **Quadrature Decoder**

The quadrature decoder decodes the filtered signals into count information. A 4X quadrature decoder is implemented, and the counter will increase or decrease by one for each signal transition. (see inset diagram)

A +1 +1 +1 +1...

Time

The decoder samples the filtered A and B signals, and calculates the up/down transition based on current and past state. When a transition is detected, either CNT<sub>UP</sub> or CNT<sub>DOWN</sub> will go high for one clock cycle. These pulses also form inputs to the internal counter.

Input line A leading line B results in counting up. Line B leading line A results in counting down.

Illegal state transitions (both signals changing between two CLK<sub>QD</sub> rising edges) will cause the count to remain constant.

#### Counter

This consists of a 22-bit binary up/down counter which counts on rising edges of the pulses output from the quadrature decoder.

When FREEZE is high, the counter's value will not change.

All 22 bits of data are passed in parallel to the shift register.

The counter is cleared to 0 asynchronously by a rising edge on  $Z_{\text{IN}}$ .

## **Shift Register**

The Shift Register operates on a separate clock to the rest of the components.

Data is latched into the shift register on a rising edge of  $CLK_{SR}$  while  $PL_{SR}$  is held high.

The LSB of the counter's value is then available immediately on CNT<sub>DATA</sub>.

On each further rising edge of  $CLK_{SR}$  (with  $PL_{SR}$  low) the next highest bit of the counter's value is latched to  $CNT_{DATA}$ .

After 21 CLK<sub>SR</sub> rising edges, further CLK<sub>SR</sub> rising edges will latch 0 to  $CNT_{DATA}$ .

At any point if  $PL_{SR}$  is held high for one rising edge of  $CLK_{SR}$  then a new count value will be latched into the shift register.

#### Zero/ Reference Mark

A rising edge on Z<sub>IN</sub> will:

- · Set the counter to have value 0

- Latch Z<sub>DATA</sub> high.

$Z_{\text{DATA}}$  will then remain high until a rising edge occurs on  $Z_{\text{RESET}}$ , which will latch  $Z_{\text{DATA}}$  low again.

If a rising edge occurs on  $Z_{\text{IN}}$ , while  $Z_{\text{RESET}}$  is high, then  $Z_{\text{DATA}}$  will still become latched high.

$Z_{\text{IN}}$  and  $Z_{\text{RESET}}$  are asynchronous input signals.

While FREEZE is high, the counter's value will be inhibited from changing.

## **Tristate Output**

All chip outputs are tristate-capable, to permit easy connection to a bus. When CS is high, all outputs become undriven. When CS is low, outputs drive their respective values.